Copyright

by

Art Ó Catháin

2008

## Modelling Flash Memory Device Behaviour using CSP

by

## Art Ó Catháin

A Dissertation submitted to the University of Dublin,

in partial fulfillment of the requirements for the degree of

Master of Science in Computer Science

2008

Modelling Flash Memory Device Behaviour using CSP

Approved by Dissertation Committee:

## Declaration

I, the undersigned, declare that this work has not previously been submitted as an exercise for a degree at this, or any other university, and that unless otherwise stated, is my own work.

Art Ó Catháin

September 5, 2008

## Permission to Lend and/or Copy

I, the undersigned, agree that Trinity College Library may lend or copy this thesis upon request.

Art Ó Catháin

September 5, 2008

## Acknowledgments

I would like to thank my supervisor Dr Andrew Butterfield and second reader Dr Arthur Hughes for their support and encouragement. Philip Armstrong from Formal Systems Europe provided invaluable support for the FDR2 refinement checking tool, without which the project would necessarily have been much more limited in scope.

I would like to attribute the following illustrations used in this document and the presentation poster:

- Yellow lightning bolt by Chris Fry from openclipart.org

- Satellite by ivak from openclipart.org

- USB stick by Gamer112 from Wikipedia

Art Ó Catháin

University of Dublin, Trinity College September 2008

## Modelling Flash Memory Device Behaviour using CSP

Publication No. \_\_\_\_\_

Art Ó Catháin University of Dublin, Trinity College, 2008

Supervisor: Dr Andrew Butterfield

Flash memory continues to progress in capacity, speed, and cost, now rivalling magnetic disks in many applications. Lack of standardization prompted leading flash memory manufacturers to form the Open NAND Flash Interface (ONFi) consortium, with the purpose of creating a standard specification.

This project examines the ONFi specification from the perspective of formal methods. Formal verification of the specification will constitute a step towards Grand Challenge 6: Dependable Systems Evolution, which aims to build systems and tools to increase the dependability and reliability of the increasingly ubiquitous computer systems that surround us.

The formal language chosen for the project was Communicating Sequential Processes (CSP), a language designed for analysing concurrency, complete with automatic model-checking tools. The ONFi specification describes a finite state machine for the internals of a compliant device, and it is this FSM that is modelled by the project.

Instead of writing CSP directly, the approach chosen was to convert the FSM's specification into an intermediate form based on State Chart XML, an XML dialect designed for specifying state machines in a machine-readable format. This XML was then automatically converted into CSP via XML Transforms (XSLT). Using XML allowed various other transformations of the specification such as conversion back to HTML to aid checking for implementation errors, and the stripping out of optional parts to leave only the mandatory specification.

Several anomalies and errors were discovered and these were communicated to ONFi. With minor adjustments to correct these, it can be argued that the specification is correct, at least for the mandatory subset of commands.

# Contents

| Ackno             | wledgments                       | vi   |

|-------------------|----------------------------------|------|

| $\mathbf{Abstra}$ | act                              | vii  |

| List of           | Tables                           | xii  |

| List of           | Figures                          | xiii |

| Chapt             | er 1 Introduction                | 1    |

| 1.1               | Flash Memory                     | 1    |

|                   | 1.1.1 NAND and NOR flash         | 1    |

| 1.2               | ONFi                             | 2    |

| 1.3               | Modelling the ONFi specification | 2    |

| 1.4               | Project aims                     | 2    |

| Chapt             | er 2 Background                  | 4    |

| 2.1               | Formal Methods                   | 4    |

|                   | 2.1.1 Refinement                 | 4    |

|                   | 2.1.2 Prevalence                 | 5    |

| 2.2               | CSP                              | 6    |

|                   | 2.2.1 Notation                   | 6    |

|                   | 2.2.2 Parallel Composition       | 6    |

|                   | 2.2.3 Choice                     | 7    |

|                   | 2.2.4 Communications             | 8    |

|                   | 2.2.5 Variables                  | 9    |

|                   | 2.2.6 Refinement                 | 9    |

|       | 2.2.7 | Practical implementations                        | 11 |

|-------|-------|--------------------------------------------------|----|

| 2.3   | Grand | l Challenges in Computing                        | 12 |

|       | 2.3.1 | Grand Challenge 6 - Dependable Systems Evolution | 12 |

| 2.4   | ONFi  | consortium                                       | 14 |

| 2.5   | ONFi  | specification                                    | 15 |

|       | 2.5.1 | Physical Interface                               | 15 |

|       | 2.5.2 | Memory organisation                              | 16 |

|       | 2.5.3 | Timing                                           | 17 |

|       | 2.5.4 | Commands                                         | 17 |

|       | 2.5.5 | Behavioural flows                                | 18 |

| Chapt | er3I  | Design                                           | 20 |

| 3.1   | CSP r | nodel                                            | 20 |

|       | 3.1.1 | Host device                                      | 20 |

|       | 3.1.2 | Communications                                   | 21 |

|       | 3.1.3 | Keeping state                                    | 23 |

|       | 3.1.4 | Minimizing state space                           | 24 |

| 3.2   | Analy | sis                                              | 24 |

|       | 3.2.1 | Deadlock freedom                                 | 24 |

|       | 3.2.2 | Livelock freedom                                 | 25 |

|       | 3.2.3 | Behavioural flows                                | 25 |

| Chapt | er4 I | mplementation                                    | 27 |

| 4.1   | Proof | of concept                                       | 27 |

|       | 4.1.1 | Host                                             | 27 |

|       | 4.1.2 | Verification                                     | 27 |

|       | 4.1.3 | Limits of prototype model                        | 28 |

| 4.2   | State | Chart XML                                        | 29 |

|       | 4.2.1 | XML languages for State Charts                   | 29 |

|       | 4.2.2 | Origins of SCXML                                 | 29 |

|       | 4.2.3 | W3C specification                                | 30 |

|       | 4.2.4 | Mapping ONFi specification to SCXML              | 31 |

|       | 4.2.5 | Apache Commons implementation                    | 33 |

|       | 4.2.6 | Adherence to SCXML standard                      | 34 |

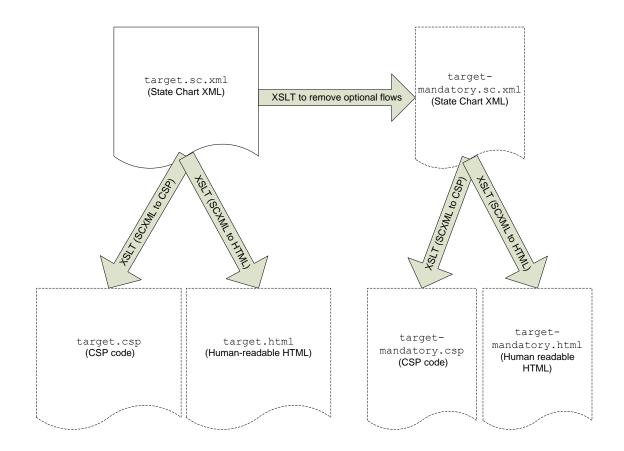

| 4.3.2       SCXML to HTML       3         4.3.3       Mandatory-only states       3         4.4       Design of the host process       3         4.4       Design of the host process       3         4.4.1       Read Command       3         4.4.2       Interleaved actions       3         4.4.3       Controlling the host       4         4.4.3       Controlling the host       4         4.5       Additional processes       4         4.5.1       Status Register bit 6       4         4.5.2       LUN 'innards' process       4         4.6       State Transitions       4         4.7       Testing       4         4.7.1       Arbitrary commands       4         4.7.2       Refinements       4         4.7.3       Non-refinements       5         5.1       Verification of ONFi specification       5         5.1.1       Ready / Busy       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.3   | 4.3                                | XML 7                                                                                                                        | Transformations                                                                                                                                                                                                                                                                                       | 34                                                                    |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

| 4.3.3       Mandatory-only states       3         4.4       Design of the host process       3         4.4.1       Read Command       3         4.4.1       Read Command       3         4.4.2       Interleaved actions       3         4.4.3       Controlling the host       4         4.5       Additional processes       4         4.5       Additional processes       4         4.5.1       Status Register bit 6       4         4.5.2       LUN 'innards' process       4         4.6       State Transitions       4         4.7       Testing       4         4.7.1       Arbitrary commands       4         4.7.2       Refinements       4         4.7.3       Non-refinements       5         5.1       Verification       5         5.1.1       Ready / Busy       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       |                                    | 4.3.1                                                                                                                        | SCXML to CSP                                                                                                                                                                                                                                                                                          | 34                                                                    |

| 4.4       Design of the host process       3         4.4.1       Read Command       3         4.4.2       Interleaved actions       3         4.4.3       Controlling the host       4         4.5       Additional processes       4         4.5       Additional processes       4         4.5       Additional processes       4         4.5       Istatus Register bit 6       4         4.5       Istatus Register bit 6       4         4.5       Istatus Register bit 6       4         4.6       State Transitions       4         4.7       Testing       4         4.7       Refinements       4         4.7.1       Arbitrary commands       4         4.7.2       Refinements       5         5.1       Verification       5         5.1       Read Parameter       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits          |                                    | 4.3.2                                                                                                                        | SCXML to HTML                                                                                                                                                                                                                                                                                         | 35                                                                    |

| 4.4.1       Read Command       3         4.4.2       Interleaved actions       3         4.4.3       Controlling the host       4         4.5       Additional processes       4         4.5       Additional processes       4         4.5.1       Status Register bit 6       4         4.5.2       LUN 'innards' process       4         4.6       State Transitions       4         4.7       Testing       4         4.7       Testing       4         4.7.1       Arbitrary commands       4         4.7.2       Refinements       4         4.7.3       Non-refinements       5         5.1       Verification of ONFi specification       5         5.1.1       Ready / Busy       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Return work       5         6.1.1       Optional commands           |                                    | 4.3.3                                                                                                                        | Mandatory-only states                                                                                                                                                                                                                                                                                 | 36                                                                    |

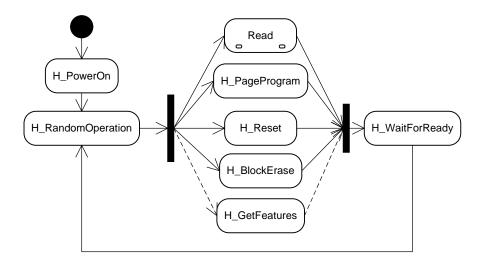

| 4.4.2       Interleaved actions       3         4.4.3       Controlling the host       4         4.5       Additional processes       4         4.5.1       Status Register bit 6       4         4.5.2       LUN 'innards' process       4         4.6       State Transitions       4         4.7       Testing       4         4.7       Testing       4         4.7       Refinements       4         4.7.2       Refinements       4         4.7.3       Non-refinements       5         5.1       Verification of ONFi specification       5         5.1       Read Parameter Page       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5 | 4.4                                | Design                                                                                                                       | of the host process                                                                                                                                                                                                                                                                                   | 36                                                                    |

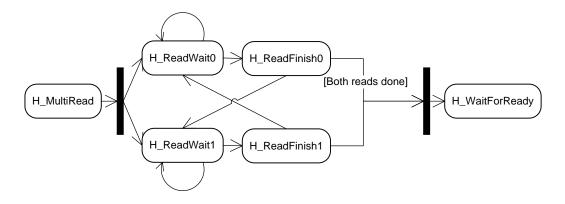

| 4.4.3       Controlling the host       4         4.5       Additional processes       4         4.5.1       Status Register bit 6       4         4.5.2       LUN 'innards' process       4         4.6       State Transitions       4         4.7       Testing       4         4.7       Testing       4         4.7.1       Arbitrary commands       4         4.7.2       Refinements       4         4.7.3       Non-refinements       5         Chapter 5       Evaluation       5         5.1       Verification of ONFi specification       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Puture work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5         |                                    | 4.4.1                                                                                                                        | Read Command                                                                                                                                                                                                                                                                                          | 39                                                                    |

| 4.5       Additional processes       4         4.5.1       Status Register bit 6       4         4.5.2       LUN 'innards' process       4         4.6       State Transitions       4         4.7       Testing       4         4.7       Testing       4         4.7.1       Arbitrary commands       4         4.7.2       Refinements       4         4.7.3       Non-refinements       5 <b>Chapter 5 Evaluation</b> 5         5.1       Verification of ONFi specification       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                       |                                    | 4.4.2                                                                                                                        | Interleaved actions                                                                                                                                                                                                                                                                                   | 39                                                                    |

| 4.5.1 Status Register bit 6       4         4.5.2 LUN 'innards' process       4         4.6 State Transitions       4         4.7 Testing       4         4.7 Testing       4         4.7.1 Arbitrary commands       4         4.7.2 Refinements       4         4.7.3 Non-refinements       4         4.7.3 Non-refinements       5         Chapter 5 Evaluation       5         5.1 Verification of ONFi specification       5         5.1.1 Ready / Busy       5         5.1.2 Status Register Update       5         5.1.3 Read Parameter Page       5         5.1.4 Reset       5         5.2 Suitability of CSP for project       5         5.3 Success of automation       5         5.4 Host process limits       5         6.1 Future work       5         6.1.1 Optional commands       5         6.1.2 ONFi version 2.0       5         6.1.3 Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                        |                                    | 4.4.3                                                                                                                        | Controlling the host                                                                                                                                                                                                                                                                                  | 40                                                                    |

| 4.5.2       LUN 'innards' process       4         4.6       State Transitions       4         4.7       Testing       4         4.7       Testing       4         4.7       Testing       4         4.7.1       Arbitrary commands       4         4.7.2       Refinements       4         4.7.3       Non-refinements       5         5       Evaluation       5         5.1       Verification of ONFi specification       5         5.1.1       Ready / Busy       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                        | 4.5                                | Additio                                                                                                                      | onal processes                                                                                                                                                                                                                                                                                        | 41                                                                    |

| 4.6       State Transitions       4         4.7       Testing       4         4.7.1       Arbitrary commands       4         4.7.2       Refinements       4         4.7.3       Non-refinements       5         Chapter 5       Evaluation       5         5.1       Verification of ONFi specification       5         5.1.1       Ready / Busy       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                             |                                    | 4.5.1                                                                                                                        | Status Register bit 6                                                                                                                                                                                                                                                                                 | 41                                                                    |

| 4.7       Testing       4         4.7.1       Arbitrary commands       4         4.7.2       Refinements       4         4.7.3       Non-refinements       5         Chapter 5       Evaluation       5         5.1       Verification of ONFi specification       5         5.1.1       Ready / Busy       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1       Variability of CSP for project       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                           |                                    | 4.5.2                                                                                                                        | LUN 'innards' process $\ldots$                                                                                                                                                                                                                                                                        | 44                                                                    |

| 4.7.1       Arbitrary commands       4         4.7.2       Refinements       4         4.7.3       Non-refinements       5         Chapter 5       Evaluation       5         5.1       Verification of ONFi specification       5         5.1.1       Ready / Busy       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                    | 4.6                                | State 7                                                                                                                      | Transitions                                                                                                                                                                                                                                                                                           | 46                                                                    |

| 4.7.2       Refinements       4         4.7.3       Non-refinements       5         Chapter 5       Evaluation       5         5.1       Verification of ONFi specification       5         5.1.1       Ready / Busy       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                          | 4.7                                | Testing                                                                                                                      | g                                                                                                                                                                                                                                                                                                     | 47                                                                    |

| 4.7.3       Non-refinements       5         Chapter 5 Evaluation       5         5.1       Verification of ONFi specification       5         5.1.1       Ready / Busy       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                 |                                    | 4.7.1                                                                                                                        | Arbitrary commands                                                                                                                                                                                                                                                                                    | 47                                                                    |

| Chapter 5 Evaluation       5         5.1       Verification of ONFi specification       5         5.1.1       Ready / Busy       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                             |                                    | 4.7.2                                                                                                                        | Refinements                                                                                                                                                                                                                                                                                           | 48                                                                    |

| 5.1       Verification of ONFi specification       5         5.1.1       Ready / Busy       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                    | 4.7.3                                                                                                                        | Non-refinements                                                                                                                                                                                                                                                                                       | 50                                                                    |

| 5.1.1       Ready / Busy       5         5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.2.1       Tractability       5         5.3       Success of automation       5         5.4       Host process limits       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                    |                                                                                                                              |                                                                                                                                                                                                                                                                                                       |                                                                       |

| 5.1.2       Status Register Update       5         5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.2.1       Tractability       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Chapte                             | er 5 E                                                                                                                       | valuation                                                                                                                                                                                                                                                                                             | 51                                                                    |

| 5.1.3       Read Parameter Page       5         5.1.4       Reset       5         5.2       Suitability of CSP for project       5         5.2.1       Tractability       5         5.3       Success of automation       5         5.4       Host process limits       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | -                                  |                                                                                                                              |                                                                                                                                                                                                                                                                                                       | <b>51</b><br>51                                                       |

| 5.1.4 Reset       5         5.2 Suitability of CSP for project       5         5.2.1 Tractability       5         5.3 Success of automation       5         5.4 Host process limits       5         6.1 Future work       5         6.1.1 Optional commands       5         6.1.2 ONFi version 2.0       5         6.1.3 Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | -                                  | Verifica                                                                                                                     | ation of ONFi specification                                                                                                                                                                                                                                                                           | 51                                                                    |

| 5.2       Suitability of CSP for project       5         5.2.1       Tractability       5         5.3       Success of automation       5         5.4       Host process limits       5         Chapter 6 Conclusions         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | -                                  | Verifica<br>5.1.1                                                                                                            | ation of ONFi specification                                                                                                                                                                                                                                                                           | $51 \\ 51$                                                            |

| 5.2.1       Tractability       5         5.3       Success of automation       5         5.4       Host process limits       5         Chapter 6       Conclusions       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | -                                  | Verifica<br>5.1.1<br>5.1.2                                                                                                   | ation of ONFi specification                                                                                                                                                                                                                                                                           | 51<br>51<br>51                                                        |

| 5.3       Success of automation       5         5.4       Host process limits       5         Chapter 6       Conclusions       5         6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | -                                  | Verifica<br>5.1.1<br>5.1.2<br>5.1.3                                                                                          | ation of ONFi specification                                                                                                                                                                                                                                                                           | 51<br>51<br>51<br>52                                                  |

| 5.4 Host process limits       5         Chapter 6 Conclusions       5         6.1 Future work       5         6.1.1 Optional commands       5         6.1.2 ONFi version 2.0       5         6.1.3 Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5.1                                | Verifica<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4                                                                                 | ation of ONFi specification                                                                                                                                                                                                                                                                           | 51<br>51<br>51<br>52<br>53                                            |

| Chapter 6 Conclusions       5         6.1 Future work       5         6.1.1 Optional commands       5         6.1.2 ONFi version 2.0       5         6.1.3 Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.1                                | Verifica<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>Suitabi                                                                      | ation of ONFi specification                                                                                                                                                                                                                                                                           | 51<br>51<br>52<br>53<br>54                                            |

| 6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.1                                | Verifica<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>Suitabi<br>5.2.1                                                             | ation of ONFi specification                                                                                                                                                                                                                                                                           | 51<br>51<br>52<br>53<br>54<br>55                                      |

| 6.1       Future work       5         6.1.1       Optional commands       5         6.1.2       ONFi version 2.0       5         6.1.3       Extending and streamlining the SCXML to CSP conversion       5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 5.1<br>5.2<br>5.3                  | Verifica<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>Suitabi<br>5.2.1<br>Success                                                  | ation of ONFi specification                                                                                                                                                                                                                                                                           | 51<br>51<br>52<br>53<br>54<br>55<br>55                                |

| 6.1.1Optional commands56.1.2ONFi version 2.056.1.3Extending and streamlining the SCXML to CSP conversion5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5.1<br>5.2<br>5.3<br>5.4           | Verifica<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>Suitabi<br>5.2.1<br>Success<br>Host p:                                       | ation of ONFi specification       .         Ready / Busy       .         Status Register Update       .         Read Parameter Page       .         Reset       .         Ility of CSP for project       .         Tractability       .         s of automation       .         rocess limits       . | 51<br>51<br>52<br>53<br>54<br>55<br>55<br>55                          |

| 6.1.2ONFi version 2.056.1.3Extending and streamlining the SCXML to CSP conversion5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 5.1<br>5.2<br>5.3<br>5.4<br>Chapte | Verifica<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>Suitabi<br>5.2.1<br>Success<br>Host pr                                       | ation of ONFi specification                                                                                                                                                                                                                                                                           | 51<br>51<br>52<br>53<br>54<br>55<br>55<br>55<br><b>57</b>             |

| 6.1.3 Extending and streamlining the SCXML to CSP conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 5.1<br>5.2<br>5.3<br>5.4<br>Chapte | Verifica<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>Suitabi<br>5.2.1<br>Success<br>Host pr<br>er 6 C<br>Future                   | ation of ONFi specification   Ready / Busy   Status Register Update   Read Parameter Page   Reset   Ility of CSP for project   Tractability   s of automation   conclusions   work                                                                                                                    | 51<br>51<br>52<br>53<br>54<br>55<br>55<br>55<br><b>57</b><br>57       |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.1<br>5.2<br>5.3<br>5.4<br>Chapte | Verifica<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>Suitabi<br>5.2.1<br>Success<br>Host pr<br>er 6 C<br>Future<br>6.1.1          | ation of ONFi specification                                                                                                                                                                                                                                                                           | 51<br>51<br>52<br>53<br>54<br>55<br>55<br>55<br><b>57</b><br>57<br>57 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5.1<br>5.2<br>5.3<br>5.4<br>Chapte | Verifica<br>5.1.1<br>5.1.2<br>5.1.3<br>5.1.4<br>Suitabi<br>5.2.1<br>Success<br>Host p:<br>er 6 C<br>Future<br>6.1.1<br>6.1.2 | ation of ONFi specification                                                                                                                                                                                                                                                                           | 51<br>51<br>52<br>53<br>54<br>55<br>55<br>55<br><b>55</b>             |

### Bibliography

| Appendix A Example State Chart XML                                                                         | 61 |

|------------------------------------------------------------------------------------------------------------|----|

| A.1 Lift                                                                                                   | 61 |

| A.1.1 SCXML representation                                                                                 | 61 |

| A.1.2 Direct use of Commons SCXML                                                                          | 61 |

| A.1.3 CSP representation                                                                                   | 61 |

| A.2 ONFI                                                                                                   | 65 |

| Appendix B Correspondence with ONFi                                                                        | 66 |

| B.1 SR[6] update $\ldots$ | 66 |

| Appendix C Technical architecture                                                                          | 67 |

| Appendix D Optimizing CSP for FDR2                                                                         | 68 |

| D.1 State space                                                                                            | 68 |

| D.2 Stack limit                                                                                            | 69 |

| D.3 Operating system and architecture                                                                      | 69 |

| Appendix E Event sequence example: Single 'Read' operation                                                 | 70 |

$\mathbf{59}$

# List of Tables

| 1.1 | NAND vs. NOR flash                                                                                   | 2  |

|-----|------------------------------------------------------------------------------------------------------|----|

| 2.1 | ONFi command set. Mandatory commands are in <b>boldface</b>                                          | 17 |

| 4.1 | SR[6] deadlock                                                                                       | 42 |

| 4.2 | Sampling $SR[6]$ within target: deadlock remains                                                     | 42 |

| 4.3 | Expected events for a Block Erase                                                                    | 48 |

| 4.4 | Expected events for a Read                                                                           | 49 |

| 4.5 | Expected events for a Page Program                                                                   | 50 |

| 5.1 | Status Register Update: event sequence for setting $SR[6]$ to $0 \ldots \ldots \ldots \ldots \ldots$ | 51 |

| 5.2 | Read Parameter Page: deadlock 1                                                                      | 52 |

| 5.3 | Read Parameter Page: deadlock 2                                                                      | 53 |

| 5.4 | Reset: deadlock 1                                                                                    | 54 |

| 5.5 | Reset: deadlock 2                                                                                    | 54 |

# List of Figures

| 1.1  | USB memory stick                                                                                         | 1  |

|------|----------------------------------------------------------------------------------------------------------|----|

| 2.1  | FDR2 refinement checker                                                                                  | 11 |

| 2.2  | Sample states from the ONFi specification                                                                | 19 |

| 3.1  | ONFi specification, p77: State variables for the Target state machine                                    | 23 |

| 4.1  | Host Processes for proof of concept model                                                                | 28 |

| 4.2  | Verifying writes are durable using $\texttt{H\_TESTREAD}$                                                | 29 |

| 4.3  | Example State Chart XML                                                                                  | 30 |

| 4.4  | Storing a date in State Chart XML                                                                        | 31 |

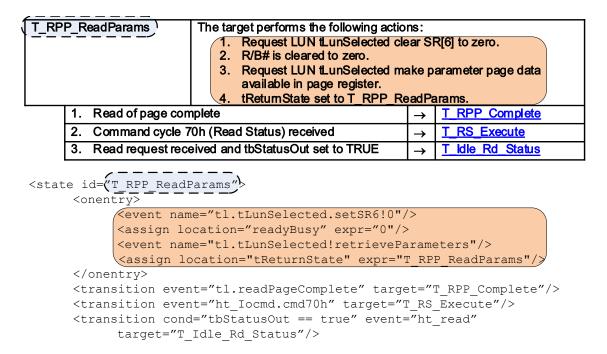

| 4.5  | Mapping ONFi specification to SCXML: state T_RPP_ReadParams $\hfill \ldots \ldots \ldots \ldots$         | 32 |

| 4.6  | Rendered HTML for three target states                                                                    | 37 |

| 4.7  | XSLT transformations of the Target state machine. Files with dotted lines are generated                  |    |

|      | automatically                                                                                            | 38 |

| 4.8  | State diagram for the host process                                                                       | 39 |

| 4.9  | State diagram for the host's Read process                                                                | 40 |

| 4.10 | State diagram for the host's MultiRead process: testing simultaneous reads on two LUNs                   | 40 |

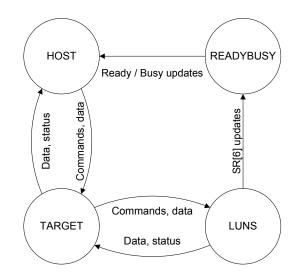

| 4.11 | Parallel CSP processes of the entire system                                                              | 43 |

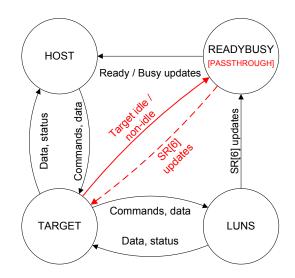

| 4.12 | Parallel CSP processes of the entire system, modified                                                    | 44 |

| 4.13 | LUN state L_RD_ArrayRead $\ldots$                                                                        | 45 |

| 4.14 | ${\rm Target \ state \ } T\_Idle\_Read  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  \dots  $ | 46 |

| 4.15 | CSP for Read refinement check                                                                            | 49 |

| A.1  | SCXML for Lift example                                                                                   | 62 |

| A.2  | Using the Apache Commons SCXML library directly with the Lift example                                    | 63 |

| A.3 | Calling the Saxon XSLT processor                           | 63 |

|-----|------------------------------------------------------------|----|

| A.4 | CSP for Lift example                                       | 64 |

| A.5 | Exploring the CSP process using Probe                      | 64 |

| A.6 | SCXML vs generated CSP code for state $T\_RPP\_ReadParams$ | 65 |

| C.1 | ONFI.csp and ONFI-mandatory.csp                            | 67 |

## Chapter 1

## Introduction

## 1.1 Flash Memory

Flash memory devices (for example, USB memory sticks) have become immensely popular in recent years. In embedded devices, flash memory has advantages over other forms of primary storage, including light weight, small physical footprint, reliability, low battery consumption, and lack of moving parts.

Figure 1.1: USB memory stick

#### 1.1.1 NAND and NOR flash

Flash memory is a form of *non-volatile* RAM: it maintains its state even when powered down, unlike conventional

computer RAM. There are two types, NAND and NOR, depending on the internal configuration of the memory cells. Which to choose depends on the individual application. Table 1.1 lists the tradeoffs between the two.

NOR's strength is its fine granularity of access: down to the level of individual bytes. NAND flash's minimum granularity is the block level which makes random access slower (the data must be read out serially). NOR tends to find more specialized uses, such as code storage, whereas NAND is popular for general storage purposes.

Inevitably, popularity entails a proliferation of standards and flash memory is no exception.

| Metric                    | NAND   | NOR    |

|---------------------------|--------|--------|

| Cost per bit              | Low    | High   |

| Capacity                  | High   | Low    |

| Active power consumption  | Low    | High   |

| Standby power consumption | High   | Low    |

| Write speed               | High   | Low    |

| Read speed                | Medium | High   |

| Access                    | Serial | Random |

Table 1.1: NAND vs. NOR flash

### 1.2 ONFi

In a recent effort to bring some standardization to the area, the Open NAND Flash Interface (ONFi) consortium created the ONFi 1.0 Specification. It lays out an interface to which flash memory devices must comply. In future, manufacturers of other devices (MP3 players, mobile phones, and so on) can rely on this interface during the design process, without having to explicitly examine the specification of their chosen brand of flash memory. It is hoped that this will increase interoperability and reduce product design times.

## 1.3 Modelling the ONFi specification

In [1], the authors created a formal model of the ONFi specification, using Z, that corresponds to the external behaviour of an ONFi-compliant device. This model is at a high level, abstracting away much of the detail of the specification. It is, as the authors acknowledge, only a start: the optional ONFi commands are not covered.

### 1.4 Project aims

The specification defines a finite state machine for a device's internal behaviour, which remains to be verified. The project will model this FSM (abstracting certain details, where appropriate) using Communicating Sequential Processes, a formal language for specifying and modelling concurrent programs. The model's behaviour should correspond to the expected external behaviour. This will be verified by checking that certain sequences of events do occur (liveness) and that other sequences are never observed (safety).

The finite state machine's definition is complex: the description takes more than twenty-five pages of text. Therefore another aim of the project is to simplify and if possible, automate, the conversion of the specification into CSP. If successful, future research could enable arbitrary finite state machines to be analysed in CSP without manual encoding.

If the model is successfully verified, it will contribute to one of the Grand Challenges of Computing: Dependable Systems Evolution. This challenge aims, over a fifteen year period, to develop a suite of tools and reference implementations that allow developers to verify that their programs are correct, using formal methods. One of the targets is a verified file system, which would be implemented on top of a verified storage layer, such as flash memory.

## Chapter 2

## Background

### 2.1 Formal Methods

The term *Formal Methods* encompasses a wide range of methods within computer science, but in general a formal system can be understood as a *specification* for a piece of software or software system, written in a language that allows for automatic reasoning and proof of correctness. Formal languages are grounded in the mathematics of set theory, and thus allow rigorous proofs.

#### 2.1.1 Refinement

Central to formal methods is the notion of *refinement*: incremental implementation of the system from the specification. The original specification should be at a suitable level of abstraction. It is not necessary to include the minute details that will be in the final program.

It is not possible to 'run' a formal specification in the way that one might run a piece of code written in a normal programming language. Instead the specification is used to constrain the *implementation*: the actual program code.

It is not feasible, in general, to construct a program directly from its specification, then prove it to be correct. Instead, the program should be constructed in small steps, each time adding more detail. Since the changes are small, it is relatively easy to prove at each stage that the implementation satisfies the specification.

Refinement is used in two ways:

• to prove *safety*: to show that the implementation will only produce the behaviours (or some subset thereof) of the specification.

• to prove *liveness*: to show that the implementation will eventually perform the all the desired behaviours.

Both properties are required for correct implementation. For example, a process that does nothing would trivially satisfy the first property (safety), but would not be much use in real life.

#### 2.1.2 Prevalence

The use of formal methods within the software industry is still quite uncommon. Possible reasons include:

Misconceptions about formal methods In [2], the author aimed to dispel some of the myths that had grown up around formal methods. The negative myths cited were:

- Formal methods are all about program proving<sup>1</sup>.

- Formal methods are only useful for safety-critical systems

- Formal methods require highly trained mathematicians.

- Formal methods increase the cost of development.

- Formal methods are unacceptable to users.

- Formal methods are not used on real, large-scale software.

- **Background of industry practitioners** Many, if not most, people in the software industry do not have a university-level computing degree, and so will not have had the opportunity to learn about formal methods.

- Lack of popular tool support The advent of Integrated Development Environments (IDEs) such as Eclipse in recent times has made programming an easier task. These IDEs allow the programmer to write, compile, and debug their code all within a single, cohesive environment. Debugging aids, keyword autocompletion, colour syntax highlighting, and so on, have greatly aided the productivity of the modern programmer.

However, despite recent advances [3], an integrated experience is not possible for a formal methods developer, who must still rely on disparate tools.

$<sup>^{1}</sup>$  in fact they are all about specification: while proofs of correctness are included, other important parts are specification writing, proving properties about the specification, and constructing programs by manipulating specifications

### 2.2 CSP

Communicating Sequential Processes is a formal language created by Anthony Hoare [4] for the purposes of modelling concurrent, communicating processes. As a formal language, it can be used for creating specifications for software, which can be verified as correct using the CSP model-checking program Failures-Divergence Refinement 2 (FDR2). The software would then be implemented in another more practical language such as Java or C++.

The basic concept in CSP is a *process* which performs *events*. An event is considered to be an atomic, indivisible action. The set of all events that a process performs is known as its *alphabet*.

#### 2.2.1 Notation

The convention is to denote events with lowercase letters and processes with uppercase letters, so for example

$a \to P$

is a process that performs the event a, and then proceeds to behave like the process P.

CSP can also be written in a machine readable form called  $CSP_m$ , consisting only of 7-bit ASCII characters. The above process has the following  $CSP_m$  representation:

Processes may be defined recursively, so for example  $P \cong a \to b \to P$  is a process that repeatedly performs the sequence of events a, b.

#### 2.2.2 Parallel Composition

CSP's usefulness stems from its ability to put processes in parallel, forcing them to synchronize on certain of their events. A process's *environment* is those events on which it must synchronise with other processes. So the process above, if required to synchronize on the event a, will wait until its environment is also willing to perform a, before proceeding like P. If the environment is unable to perform the event a, the process is *deadlocked*. In CSP the process named *STOP* is the canonical deadlocked process, unable to perform any events at all. The notation for parallel composition is as follows:

| Normal CSP          | $\mathrm{CSP}_m$ |

|---------------------|------------------|

| $P_A \parallel_B Q$ | P [ A    B ] Q   |

Here P and Q are processes; A and B are sets of events on which P and Q, respectively, are required to synchronize. The *interface* of a process is the set of events in its alphabet on which it is required to synchronize. If A is P's alphabet and B is Q's alphabet, then the above can be written more simply as  $P \parallel Q$ .

If A and B share no common events, then P and Q are said to be interleaved. This is written  $P \parallel \mid Q$ .

#### Example

Consider three processes, P, Q, and R, as follows:

$$P \stackrel{\widehat{=}}{=} a \rightarrow b \rightarrow P$$

$$Q \stackrel{\widehat{=}}{=} b \rightarrow a \rightarrow Q$$

$$R \stackrel{\widehat{=}}{=} a \rightarrow R$$

$P \parallel R$  will perform  $a, b, a, b, \dots$  and so on.

$P \parallel Q$  will deadlock, since P is willing to perform only a, and Q is willing to perform only b.

$Q \parallel R$  will not deadlock, since Q can perform its b event immediately. R is not required to synchronize on b since it is not part of R's alphabet.

#### 2.2.3 Choice

Any realistic formal language must be able to represent conditional branches in the program flow, and for this CSP uses the notion of choice.

#### **External Choice**

The following process behaves like either P or Q, depending on the next event that takes place in the process's environment:

$$P \Box Q$$

If P and Q are defined as in the previous section, then the environment's choosing a will cause the process to behave like P and also perform a (then b, if the environment allows it, since that is P's next event).

#### Internal Choice

Processes may also make *internal choice*, in which case the environment has no effect on which path is taken:

$P \sqcap Q$

The choice between P and Q here is nondeterministic. This non-determinism is often exploited by specifications in order to avoid over-constraining any implementation.

#### 2.2.4 Communications

Thus far only events with a single label (a, b, etc.) have been introduced. CSP allows more sophisticated communication to take place between processes, using *channels*. (In fact, a, b, above are also channels: the simplest kind of channel, with only one type of event and no data being passed.)

Channels can carry information in the form of integers, booleans, and user-defined types (defined by the datatype keyword). They are bidirectional: a process can choose to 'receive' or 'send' on a particular channel.

#### Examples

Channel definition (in  $CSP_M$  notation):

• A channel that passes integers:

channel a:Int

• A channel that passes both a boolean and an integer value at once:

channel b:Bool.Int

• A channel that sends a custom datatypes:

datatype Languages = english | french | irish channel lang:Languages

Use of channels by processes:

• A process P, which repeatedly sends some information on the channel b, above:

$P \mathrel{\widehat{=}} b.\mathit{false}.10 \to P$

#### Hiding

It is often desirable to 'hide' events: define a process with a certain interface, but only expose a subset of that interface to its environment. The remaining events are now *internal*, and are not seen at all by the process's environment. This is often used during refinement checking (as described in section 2.2.6), to abstract away the irrelevant internal details of an implementation.

#### 2.2.5 Variables

Variable declaration and assignment, as used in procedural languages, are not possible in CSP. Instead, state can be maintained by passing parameters to CSP processes.